High-Reliability, Radiation-Tolerant, Antifuse-Based FPGAs

Features

- Highly reliable, nonvolatile antifuse technology

- Up to 840 user I/Os

- Up to 540 kbits of embedded memory with optional EDAC protection

- Hermetically sealed packages for space applications (CQFP, CCGA/LGA)

Radiation Tolerance

- Total dose: 300 krad (functional) and 200 krad (parametric)

- SEU less than 1E-10 errors per bit-day (worst-case GEO)

- SEL immune to LETTH more than 117 MeV-cm2/mg

- SEU immune to LETTH > 37 MeV-cm2/mg

Qualification

- QML class Q and QML class V qualification

- Heritage in many major programs including Sentinel-2, KOMPSAT-3, ExoMars, GOES-R, Galileo, BepiColombo, MTG, James Webb Space Telescope, GPS III, Iridium and more

Space

Radiation and Reliability

Radiation-Tolerant FPGAs

Sub-QML FPGAs

- Application Notes

- Data Sheets

- Handbooks

- White Papers

- Power Estimator

- Radiation Reports

- Product Selector Guide

Data Sheets

|

Title

|

Date

|

|---|---|

| RTAX-S/SL and RTAX-DSP Radiation-Tolerant FPGAs Datasheet | 11 Dec 2023 |

| PD3068: Package Mechanical Drawings Datasheet | 17 Apr 2025 |

| CQ352 Pin Name List | 18 Aug 2022 |

| CG1152 Pin Name List | 18 Aug 2022 |

| CG1272 Pin Name List | 18 Aug 2022 |

| CG624 Pin Name List | 18 Aug 2022 |

| CQ208 Pin Name List | 18 Aug 2022 |

| CQ256 Pin Name List | 18 Aug 2022 |

IBIS Models

|

Title

|

Date

|

|---|---|

| RTAX-S/SL IBIS Model (UNIX gzip) | 06 Mar 2005 |

Note:

- IBIS Model Usage provides instructions on obtaining max/min source/sink current.

- IBIS Background and Usage Application Notes provides signal integrity on PCBs.

BSDL Models

|

Title

|

Date

|

|---|---|

| RTAX250S-CG624 BSDL | 12 May 2010 |

| RTAX2000S-CG1152 BSDL | 17 Jun 2007 |

| RTAX1000S-CG624 BSDL | 28 Mar 2005 |

| RTAX1000S-CQ352 BSDL | 28 Mar 2005 |

| RTAX2000S-CG624 BSDL | 28 Mar 2005 |

| RTAX2000S-CQ256 BSDL | 26 Jul 2006 |

| RTAX2000S-CQ352 BSDL | 28 Mar 2005 |

| RTAX4000S-CQ352 BSDL | 12 May 2010 |

| RTAX250S-CQ208 BSDL | 28 Mar 2005 |

| RTAX250S-CQ352 BSDL | 28 Mar 2005 |

| RTAX4000D-CG1272 BSDL | 03 Aug 2010 |

| RTAX2000D-CG1272 BSDL | 18 Jan 2018 |

| RTAX2000D-CQ352 BSDL | 18 Jan 2018 |

| RTAX4000D-CQ352 BSDL | 03 Aug 2010 |

Packaging Data

|

Title

|

Date

|

|---|---|

| CG1152 Daisy Chain Package Drawing | 21 Jun 2010 |

| CG1272 Daisy Chain Package Drawing | 21 Jun 2010 |

| CG624 Daisy Chain Package Drawing | 21 Jun 2010 |

| Package Thermal Characteristics and Weights | 05 Jun 2003 |

| Hermetic Package MechanicalConfiguration | 15 Jan 2003 |

DSP Core Handbook

|

Title

|

Date

|

|---|---|

| RTAX-DSP Cores: SmartGen Hard Multiplier Adder/Subtractor Handbook | 08 Jun 2009 |

| RTAX-DSP Cores: SmartGen Hard Multiplier Accumulator Handbook | 08 Jun 2009 |

| RTAX-DSP Cores: SmartGen Hard Multiplier Handbook | 08 Jun 2009 |

White Papers

|

Title

|

Date

|

|---|---|

| Power Supply Transients on RTAX-S and RTSX-SU Devices White Paper | 13 Feb 2020 |

| RTAX-S Testing and Reliability Update | 13 Sep 2006 |

| Enhanced Qualification and Lot Acceptance Procedures | 25 Aug 2005 |

|

Title

|

Date

|

|---|---|

| Power Estimator | 14 Oct 2022 |

| RTAX-S/SL/DSP Power-On Reset and Brown-Out Device Behavior FAQs | 23 Jul 2014 |

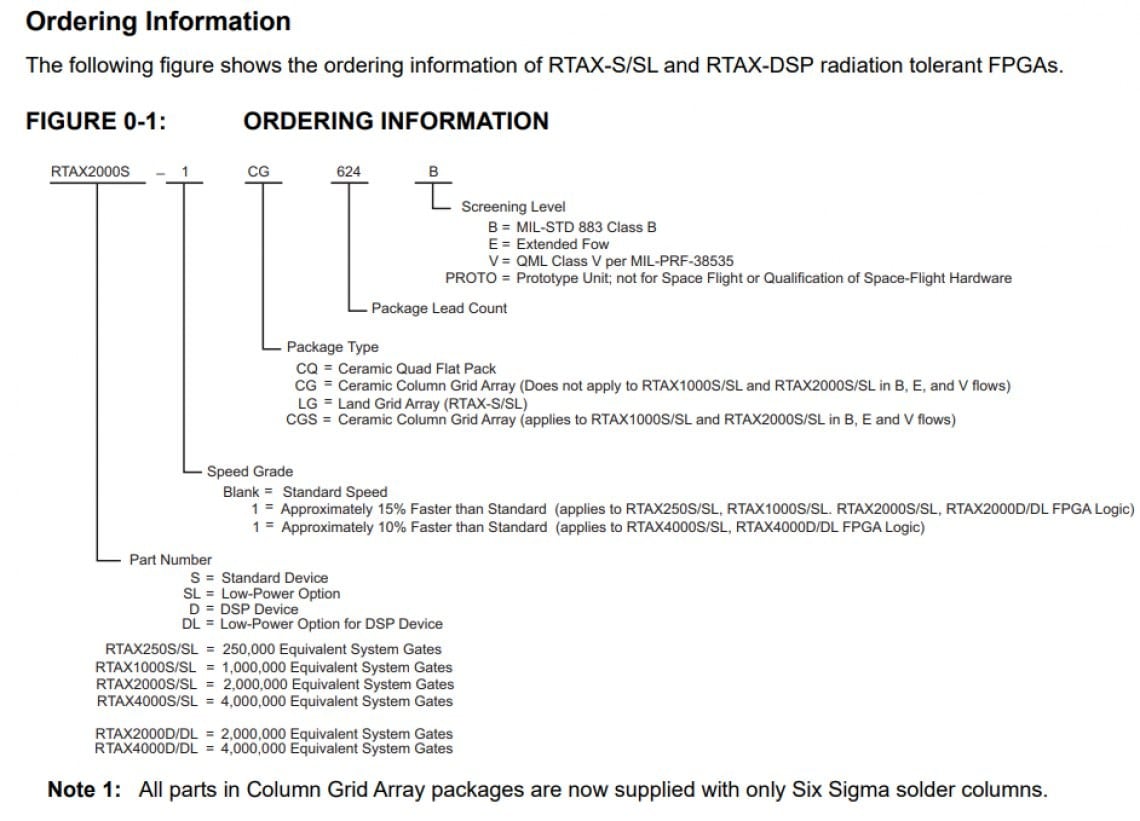

RTAX-S/SL and RTAX-DSP

RTAX-S/SL radiation-tolerant FPGAs offer industry-leading advantages for designers of spaceflight systems. High performance, low power consumption, true single-chip form factor, and live-at-power-up operation all combine to make RTAX-S/SL devices the FPGAs of choice for space designers. RTAX-DSP spaceflight FPGAs add embedded radiation-tolerant, multiply-accumulate blocks to the tried-and-trusted industry standard RTAX-S/SL product family. The result is a dramatic increase in device performance and utilization when implementing arithmetic functions (such as those encountered in DSP algorithms) without sacrificing reliability or radiation tolerance. RTAX-DSP integrates complex DSP functions into a single device without any external components for code storage or multiple-chip implementations for radiation mitigation.

Notes:

- All parts in Column Grid Array packages are now supplied with only six sigma solder columns

Programmers and Adapters

Silicon Sculptor 4

This is a CE-compliant production device programmer.

Silicon Sculptor Adapter Module

Silicon sculptor adapter modules are package specific. They depend on the product family, but are independent of gate count.

In-House-Programming

An optional In-House Programming (IHP) service is available if you are purchasing our devices in large volumes.