Log in to myMicrochip to access tools and benefits. Sign up in just one minute.

Maximize Your Experience: Reap the Personalized Advantages by Completing Your Profile to Its Fullest! Update Here

Stay in the loop with the latest from Microchip! Update your profile while you are at it. Update Here

Complete your profile to access more resources.Update Here!

Search Documentation

|

Document Category

Title

Date

|

Data Sheets

16 Jan 2003

|

|

Document Category

Title

Date

|

Product Selector Tools

29 Aug 2013

|

|

Document Category

Title

Date

|

Data Sheets

30 Sep 2024

|

|

Document Category

Title

Date

|

Data Sheets

17 Apr 2025

|

|

Document Category

Title

Date

|

Packaging Specifications

05 Jun 2003

|

|

Document Category

Title

Date

|

Packaging Specifications

15 Jan 2003

|

|

Document Category

Title

Date

|

Product Brief

14 Oct 2022

|

|

Document Category

Title

Date

|

07 Oct 2022

|

|

Document Category

Title

Date

|

Data Sheets

23 Sep 2022

|

|

Document Category

Title

Date

|

Application Notes

12 Jan 2003

|

|

Document Category

Title

Date

|

Application Notes

12 Jan 2003

|

|

Document Category

Title

Date

|

Application Notes

13 Jan 2003

|

|

Document Category

Title

Date

|

Application Notes

15 Jul 2004

|

|

Document Category

Title

Date

|

Application Notes

07 Aug 2003

|

|

Document Category

Title

Date

|

Application Notes

18 Aug 2003

|

|

Document Category

Title

Date

|

Application Notes

16 Jul 2003

|

|

Document Category

Title

Date

|

Application Notes

22 Jul 2004

|

|

Document Category

Title

Date

|

Application Notes

28 Mar 2005

|

|

Document Category

Title

Date

|

Application Notes

23 Feb 2005

|

|

Document Category

Title

Date

|

Application Notes

07 Aug 2003

|

|

Document Category

Title

Date

|

Application Notes

21 Sep 2004

|

|

Document Category

Title

Date

|

Application Notes

21 Jul 2004

|

|

Document Category

Title

Date

|

Application Notes

08 Feb 2005

|

|

Document Category

Title

Date

|

Application Notes

23 Jun 2005

|

|

Document Category

Title

Date

|

Application Notes

06 May 2013

|

|

Document Category

Title

Date

|

Application Notes

20 Jul 2003

|

|

Document Category

Title

Date

|

Application Notes

25 May 2003

|

|

Document Category

Title

Date

|

Application Notes

13 Oct 2004

|

|

Document Category

Title

Date

|

Application Notes

22 Jun 2006

|

|

Document Category

Title

Date

|

Application Notes

22 Sep 2010

|

|

Document Category

Title

Date

|

Application Notes

07 Aug 2003

|

|

Document Category

Title

Date

|

Application Notes

30 Oct 2011

|

|

Document Category

Title

Date

|

Application Notes

18 Mar 2025

|

|

Document Category

Title

Date

|

Application Notes

18 May 2004

|

|

Document Category

Title

Date

|

Application Notes

15 Jan 2003

|

|

Document Category

Title

Date

|

Application Notes

13 Feb 2003

|

|

Document Category

Title

Date

|

Application Notes

25 May 2003

|

|

Document Category

Title

Date

|

Application Notes

02 Aug 2011

|

|

Document Category

Title

Date

|

Board Design Files

06 Mar 2005

|

|

Document Category

Title

Date

|

Board Design Files

06 Mar 2005

|

|

Document Category

Title

Date

|

Board Design Files

06 Mar 2005

|

|

Document Category

Title

Date

|

Board Design Files

28 Mar 2005

|

|

Document Category

Title

Date

|

Board Design Files

28 Mar 2005

|

|

Document Category

Title

Date

|

Board Design Files

28 Mar 2005

|

|

Document Category

Title

Date

|

Board Design Files

28 Mar 2005

|

|

Document Category

Title

Date

|

Board Design Files

28 Mar 2005

|

|

Document Category

Title

Date

|

BSDL Files

10 Oct 2019

|

|

Document Category

Title

Date

|

Board Design Files

28 Mar 2005

|

|

Document Category

Title

Date

|

Board Design Files

28 Mar 2005

|

|

Document Category

Title

Date

|

Board Design Files

28 Mar 2005

|

|

Document Category

Title

Date

|

Board Design Files

28 Mar 2005

|

|

Document Category

Title

Date

|

Board Design Files

28 Mar 2005

|

|

Document Category

Title

Date

|

Board Design Files

28 Mar 2005

|

|

Document Category

Title

Date

|

BSDL Files

10 Oct 2019

|

|

Document Category

Title

Date

|

BSDL Files

10 Oct 2019

|

|

Document Category

Title

Date

|

BSDL Files

10 Oct 2019

|

|

Document Category

Title

Date

|

Board Design Files

28 Mar 2005

|

|

Document Category

Title

Date

|

Board Design Files

28 Mar 2005

|

|

Document Category

Title

Date

|

Board Design Files

28 Mar 2005

|

|

Document Category

Title

Date

|

Board Design Files

26 Jul 2006

|

|

Document Category

Title

Date

|

Board Design Files

28 Mar 2005

|

|

Document Category

Title

Date

|

BSDL Files

10 Oct 2019

|

|

Document Category

Title

Date

|

BSDL Files

10 Oct 2019

|

- Application Notes

- Data Sheets

- Power Estimator

- User Guides

- Product Selector Guide

Data Sheets

|

Title

|

Date

|

|---|---|

| Axcelerator Family FPGAs Product Brief | 16 Jan 2003 |

| Antifuse Product Catalog | 29 Aug 2013 |

| Axcelerator Family FPGAs Datasheet | 30 Sep 2024 |

| PD3068: Package Mechanical Drawings Datasheet | 17 Apr 2025 |

IBIS Models

|

Title

|

Date

|

|---|---|

| Axcelerator Commercial IBIS Model (UNIX gzip) | 06 Mar 2005 |

| Axcelerator Industrial IBIS Model (UNIX gzip) | 06 Mar 2005 |

| Axcelerator Military IBIS Model (UNIX gzip) | 06 Mar 2005 |

Note:

- IBIS Model Usage provides instructions on obtaining max/min source/sink current.

- IBIS Background and Usage Application Notes provides signal integrity on PCBs.

BSDL Models

|

Title

|

Date

|

|---|---|

| AX125-CS180 BSDL | 28 Mar 2005 |

| AX125-FG324 BSDL | 28 Mar 2005 |

| AX250-CQ208 BSDL | 28 Mar 2005 |

| AX250-FG256 BSDL | 28 Mar 2005 |

| AX250-FG484 BSDL | 28 Mar 2005 |

| AX250_CQ352.BSDL | 10 Oct 2019 |

| AX1000-BG729 BSDL | 28 Mar 2005 |

| AX1000-CG624 BSDL | 28 Mar 2005 |

| AX1000-CQ352 BSDL | 28 Mar 2005 |

| AX250-PQ208 BSDL | 28 Mar 2005 |

| AX500-CQ352 BSDL | 28 Mar 2005 |

| AX500-FG484 BSDL | 28 Mar 2005 |

| AX500_CQ208 BSDL | 10 Oct 2019 |

| AX500_FG676 BSDL | 10 Oct 2019 |

| AX500_PQ208 BSDL | 10 Oct 2019 |

| AX1000-FG484 BSDL | 28 Mar 2005 |

| AX1000-FG896 BSDL | 28 Mar 2005 |

| AX2000-CG624 BSDL | 28 Mar 2005 |

| AX2000-CQ256 BSDL | 26 Jul 2006 |

| AX2000-CQ352 BSDL | 28 Mar 2005 |

| AX1000_FG676 BSDL | 10 Oct 2019 |

| AX2000_FG896 BSDL | 10 Oct 2019 |

|

Title

|

Date

|

|---|---|

| Package Thermal Characteristics and Weights | 05 Jun 2003 |

| Hermetic Package MechanicalConfiguration | 15 Jan 2003 |

| Power Estimator | 14 Oct 2022 |

|

Title

|

Date

|

|---|---|

| Overview of Antifuse Device Security- White Paper | 07 Oct 2022 |

| DC-DC Regulator Guide for Microsemi FPGAs and SOC FPGAs | 23 Sep 2022 |

The Axcelerator FPGA family is a single-chip, nonvolatile solution offering high performance and unprecedented design security at densities of up to 2 million equivalent system gates. Utilizing the AX architecture, Axcelerator devices have several system-level features, such as embedded SRAM (with embedded FIFO control logic), PLLs, segmentable clocks, chip-wide highway routing and carry logic. The solution is based on a 0.15-μm, seven-layers-of-metal CMOS antifuse process technology and 350-MHz system performance.

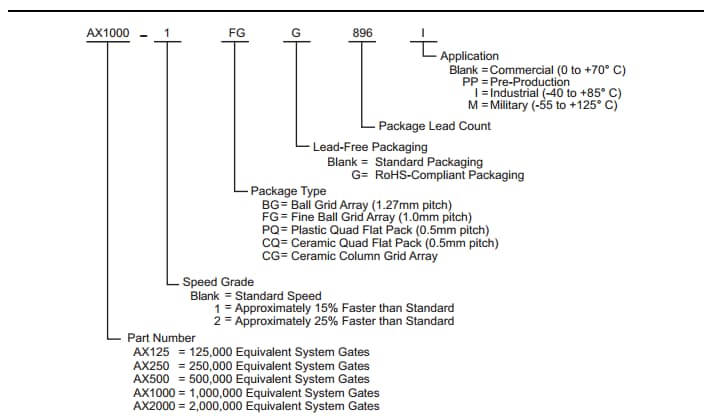

Refer to the image below to find the product that best meets your specifications.