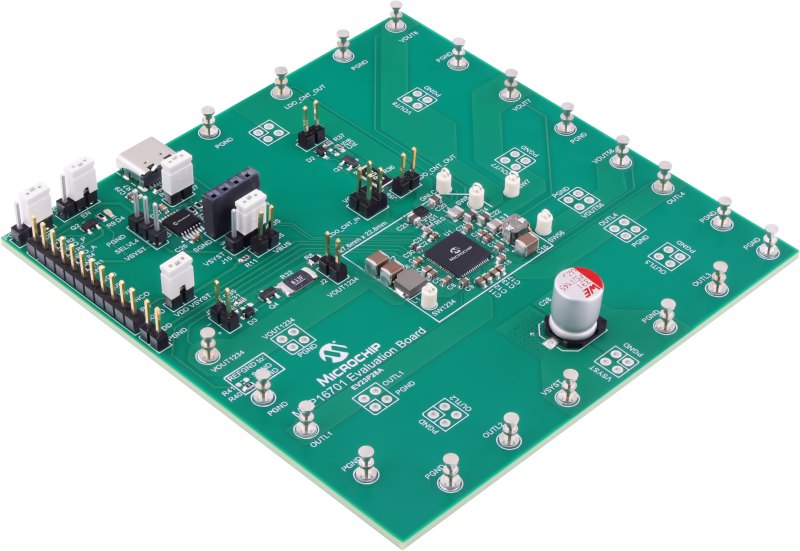

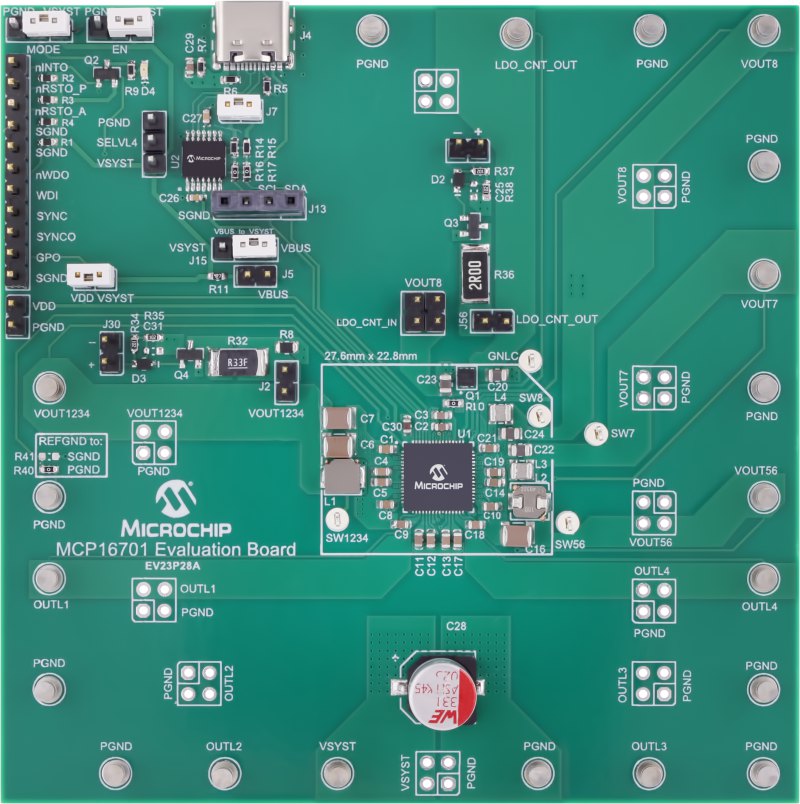

Part Number: EV23P28A

MCP16701 Evaluation Board

• Input Voltage: 2.7V to 5.5V

• Eight 1.5A Buck DC-DC Channels

• Four 300 mA High-Accuracy LDOs

• One High-Accuracy, High-PSRR LDO Controller Using External N-channel MOSFET

• 100% Duty Cycle Capability of Buck Channels

• Reference Ground (REFGND) is Routed to Bucks1-4 for an Improved Accuracy of the Output Voltage

• Low-Noise Forced-PWM and Light-Load High-efficiency Mode Available (Pin-Selectable or Bit Control)

• External Synchronization of Switching Frequency; this Feature can be Active or Disabled in Registry

• Selectable Phase (0°, 90°, 180° or 270°) for Buck Channels

• Global RESET (nRSTO_A) with Programmable De-Assertion Delay

• User-Defined RESET (nRSTO_P) with Programmable De-Assertion Delay

• 1 MHz MCP2221 I2C Interface => 400kHz MCP2221 I2C Interface

• On Die Programmable NVM

• NVM Write Password Protection (e.g., Voltage Setting)

• Dedicated VDD Supply Pin for NVM and Interface Allows Programming without Powering Up the Application

• Re-Configurable During Runtime

• Hiccup-Mode Current Limit for Buck Channels (can be Disabled)

• Programmable thermal early warning and thermal shutdown protection

• LED Visual Indicator for the nINTO Pin (Interrupt Flag) with Selectable Interrupt Masking for Each Channel

• On-Board Load Transient Generator for VOUT1234 and LDOC_OUT

• General Purpose Output (GPO)

• Watchdog Timer

Overview

The MCP16701 is a Power Management Integrated Circuit (PMIC) dedicated to FPGA and high-end MPU applications. It supports commercial and industrial applications. The MCP16701 integrates eight parallelable DC-DC buck regulators, four auxiliary LDOs and one low-input/low-output voltage LDO controller using an external MOSFET. It also features an interrupt flag that signals faults and a 3.4 MHz I2C interface. They can be operated either independently or in paralleled groups of up to four to support higher currents. The LDOs can also be cascaded (in groups of two) to the output of a DC-DC channel, thus improving overall conversion efficiency. The MCP16701 power management settings allow for the implementation of low-power mode commanded by a GPIO pin (MODE input of MCP16701). Any channel can also be selectively and permanently set in Auto PFM or FPWM. Active discharge resistors are provided on each output. All Buck channels and LDOs support soft start-up.