Overview of LX4580 Serial Interfaces and Bus Error Management

Learn more about the LX4580 analog front-end Integrated Circuit (IC) for actuation systems and its dual serial interfaces and error-detecting and correcting architecture.

LX4580 Serial Interfaces and Bus Error Management

This is the fifth article in a series discussing topics around LX4580 implementations. The LX4580 is an analog front end designed for high-reliability motor-actuator control systems that must comply with stringent standards such as DO-160 for avionics in airborne systems. The LX4580 interfaces with dual microcontrollers (MCUs) or Field-Programmable Gate Arrays (FPGAs) in redundant COM/MON system architectures and features ECC encoding to provide 1-bit error correction and 2-bit error detection. Sequential logic is implemented with Triple Mode Redundancy (TMR) to protect against Single-Event Upsets (SEUs).

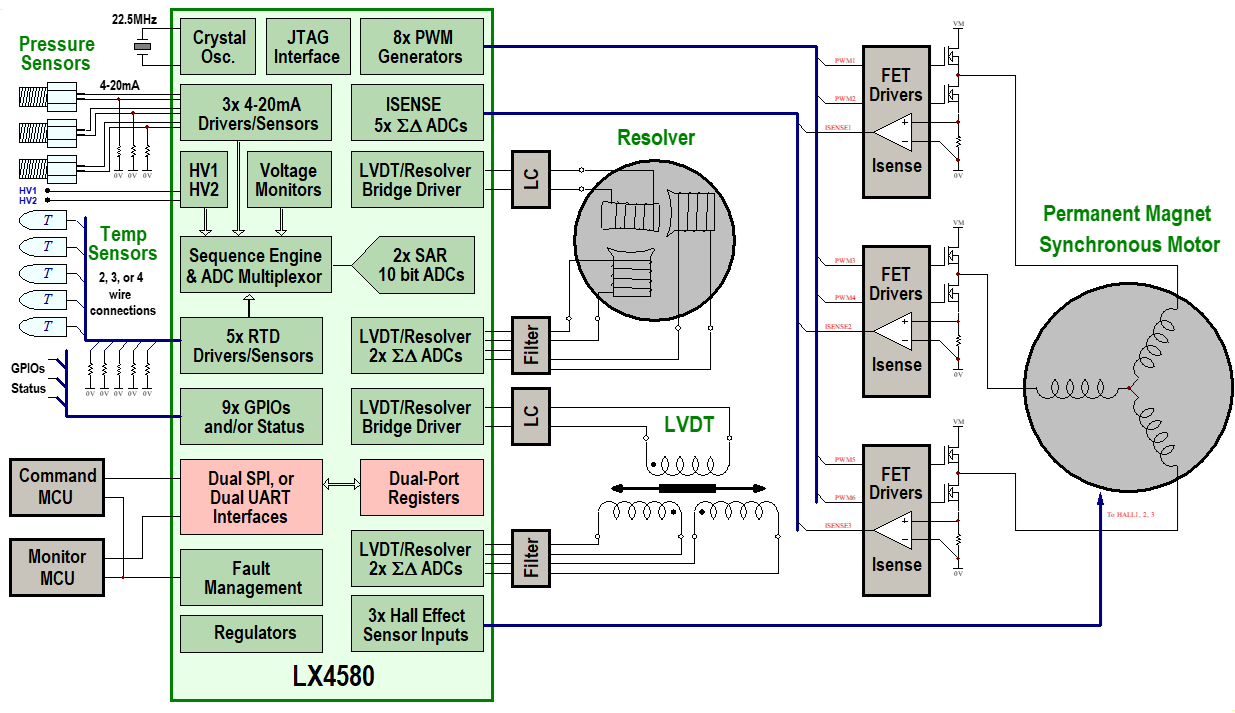

The block diagram below illustrates a typical Permanent Magnet Synchronous Motor (PMSM) motor-actuator system using redundant Linear Variable Differential Transformers (LVDTs) for actuator linear position feedback. The LX4580 combines analog sensor acquisition and motor control Pulse-Width Modulation (PWM) synthesis. Motor current sensing and LVDT secondary waveform acquisition use a dedicated Σ-Δ ADC per channel, nine in total. The LX4580 also includes sensor interfaces, which use a state machine and a pair of 10-bit Successive-Approximation-Register Analog-to-Digital Converters (SAR ADCs) for digitizing. This article provides an overview of the dual serial interfaces that interface with the internal registers and discusses the error-detecting and correcting architecture. These blocks are highlighted in pink in the block diagram.

Figure 1. Typical PMSM System

|

The LX4580 offers two serial interfaces, each with simultaneous and asynchronous dual-port read/write access to the register set. The dual interfaces enable the control system to implement a classic COM/MON architecture. This setup allows a main (command) processor to operate an actuator, while a second (monitor) processor examines the same measurement data to double-check the command processor's actions. A bus between the two processors shares measurement and control data for comparison.

The LX4580's serial interfaces can be configured via a pin to operate in either asynchronous mode (using two pins: TXD and RXD) or synchronous SPI mode (using four pins: SS, CLK, MOSI and MISO). The SPI interfaces are fast, up to 30MHz and generally preferable. The asynchronous alternative is limited to 1MHz but is easier to operate over long wiring harnesses since there is no timing relationship between the bus lines.

A single command from a serial interface host to an LX4580 comprises four 16-bit SPI packets. For the asynchronous interface option, each 16-bit packet is further split into two 8-bit chunks (plus start, parity and stop bits). Each 16-bit packet comprises 11 payload bits and 5 parity bits as a Hamming 16-11 Error Correction Code (ECC) implementation. This Hamming code is Single-Error Correcting and Double-Error Detecting (SECDED) due to the inclusion of the fifth parity bit. This means that for every 16-bit communication, a single bit error is guaranteed to be detected and corrected, ensuring data integrity. If the 16-bit packet has two flipped bits, the packet won't be corrected, but the transmission error will be detected. In this case, the uncorrectable packet is ignored. The LX4580's FAULT pin alerts the host, and an internal register identifies the issue.

It's worth comparing the LX4580's Hamming code with conventional parity error detection. Single-bit parity adds an extra bit to a packet (so a 16-bit word would become 17 bits) to indicate whether there are an even or odd number of 1s in the packet. It guarantees to detect a single bit error anywhere in the packet (including the parity bit) but doesn't identify the bit. This provides single-bit error detection but not correction. Unfortunately, single-bit parity guarantees not to detect a packet with any two bits at fault. This is because two flipped bits have the same parity as no flipped bits. Single-bit parity is useful where single-bit errors are rare, multiple-bit errors very rare and data integrity is not especially critical (such as printer output). As a further note, single-bit parity actually guarantees to detect any odd numbers of bit errors (1, 3, 5…), but will not detect any even numbers of bit errors (2, 4, 6…).

The fundamental 4-packet structure for LX4580 register write-access is shown in Figure 2 below. The first bit of every packet is 0, indicating that the packet is from the host. The next two bits are Packet ID bits, which identify which of the four types of packets it is. The next 8 bits are the packet's payload, which includes Command {C0:C3}, 12-bit register address {A0:A11} and 16-bit register data {D0:D15}. The final 5 bits are Hamming parity bits {P0:P4}.

Figure 2. 4-Packet Serial Interface Transmission from Host to LX4580 (Register-Write)

Packet |

D0 |

D1 |

D2 |

D3 |

D4 |

D5 |

D6 |

D7 |

D8 |

D9 |

D10 |

D11 |

D12 |

D13 |

D14 |

D15 |

0 |

Packet ID |

Parity |

||||||||||||||

First Command {C0:C3} Address {A0:A3} |

0 |

0 |

0 |

C0 |

C1 |

C2 |

C3 |

A0 |

A1 |

A2 |

A3 |

P0 |

P1 |

P2 |

P3 |

P4 |

2nd Address {A4:A11} |

0 |

1 |

0 |

A4 |

A5 |

A6 |

A7 |

A8 |

A9 |

A10 |

A11 |

P0 |

P1 |

P2 |

P3 |

P4 |

3rd Data {D0:D7} |

0 |

0 |

1 |

D0 |

D1 |

D2 |

D3 |

D4 |

D5 |

D6 |

D7 |

P0 |

P1 |

P2 |

P3 |

P4 |

Last Data {D8:D15} |

0 |

1 |

1 |

D8 |

D9 |

D10 |

D11 |

D12 |

D13 |

D14 |

D15 |

P0 |

P1 |

P2 |

P3 |

P4 |

For LX4580 register read access, the last two packets are data read from the LX4580, as shown in Figure 3 below. Each packet contains 10 data bits as opposed to just a byte, which allows the results of the LX4580's 10-bit ADCs, for example, to be read in one packet.

Figure 3. Final 2 Packets Transmitted from LX4580 to Host for Register-Read

Packet |

D0 |

D1 |

D2 |

D3 |

D4 |

D5 |

D6 |

D7 |

D8 |

D9 |

D10 |

D11 |

D12 |

D13 |

D14 |

D15 |

Data Ready |

Parity |

|||||||||||||||

3rd Data D8-D9,{D0:D7} |

1 |

D8 |

D9 |

D0 |

D1 |

D2 |

D3 |

D4 |

D5 |

D6 |

D7 |

P0 |

P1 |

P2 |

P3 |

P4 |

Last Data {D6:D15} |

1 |

D6 |

D7 |

D8 |

D9 |

D10 |

D11 |

D12 |

D13 |

D14 |

D15 |

P0 |

P1 |

P2 |

P3 |

P4 |

The 4-bit Command nibble is the key to optimizing efficient use of the serial interface, reducing register addressing overhead and unnecessary data transfers to a minimum. The 4 bits select register access options as follows:

- Read or write just the lower byte of a register in a 3-packet transaction

- Read or write just the upper byte of a register in a 3-packet transaction

- Read or write both the lower byte and the upper byte of a register in a 4-packet transaction

- Read or write just the lower byte of sequential registers in a 3-packet transaction for the first register, plus a single packet for subsequent registers (address auto-incrementing)

- Read or write just the upper byte of sequential registers in a 3-packet transaction for the first register, plus a single packet for subsequent registers (address auto-incrementing)

- Read or write both the lower byte and the upper byte of a register in a 4-packet transaction for the first register, plus two packets for subsequent registers (address auto-incrementing)

The optional byte or word access avoids unnecessary data, while the address auto-incrementing allows a bank of data to be accessed with the minimum overhead of just sending the initial address. In systems that don't need dual processor access to an LX4580, both buses could be used by a single processor. This allows one code section to be interrupt-based using one bus without concern for the main code body using the other bus asynchronously.

The LX4580 is currently available for sampling, with an evaluation board also available. Product information can be found on the LX4580 web page.

For additional information, please contact Dorian Johnson, Product Marketing Manager for Mixed-Signal Aerospace Products, at Dorian.Johnson@microchip.com.

Want More?

Check out the previous posts in this series:

Part One (Selecting MOSFET Drivers for the LX4580 Analog Front-End IC for Motor-Actuator Control Systems)

Part Two (Motor Current Sensing With the LX4580 Motor Controller and Data Acquisition System)

Part Three (Overview of LX4580 Sensor Support and Sensor Fault Detection)

Part Four (Overview Of LX4580 Power Supplies and Supply Fault Management)