Support for Microchip’s RISC-V Platforms in Antmicro’s Open-Source Renode Framework and Beyond

Antmicro and Microchip's consistent partnership enables a complete Renode-based simulation platform for the Mi-V ecosystem.

Complete Renode-Based Simulation Platform for the Mi-V Ecosystem

Antmicro has been cooperating with Microchip for many years now, enabling Microchip’s Mi-V ecosystem with its simulation solutions. Both companies are founding members of RISC-V International and have been driving the RISC-V free and open Instruction Set Architecture (ISA) ecosystem since the early days.

Since the beginning of this ongoing collaboration, Antmicro and Microchip have been working hand in hand, providing a complete Renode-based simulation platform for the Mi-V ecosystem, including both Mi-V soft Central Processing Units (CPUs) and the highly advanced multi-core PolarFire® System-on-Chip Field-Programmable Gate Array (SoC FPGA), capable of co-simulation enabling rapid co-development of software and FPGA code.

Renode—Antmicro’s Advanced Simulation Framework

Renode is Antmicro’s open-source simulator capable of accelerating any development stage of Internet of Things (IoT) and embedded systems. It allows you to build virtual SoCs using a wide range of peripherals and CPUs of various architectures, like Arm® or RISC-V. Renode offers a wide range of features, including co-simulation between fast models of your core system—such as the hard blocks of Microchip PolarFire SoC FPGAs and a specific peripheral or subsystem that is developed in the PolarFire SoC FPGA fabric—directly from HDL. This significantly speeds up your system development in complex scenarios, as functional simulations are noticeably faster than HDL simulations.

Thanks to Renode’s advanced debugging and testing capabilities, you can catch bugs earlier in the development cycle and get greater control over your target platform and its environment. Renode can also be used during the pre-silicon stage of a project, as has been done by Microchip to enable software development for their PolarFire SoC FPGA before it was physically built and distributed.

PolarFire SoC and Icicle in Renode

The collaboration of Antmicro and Microchip helped us reach a significant milestone in Renode’s history. You can find the GitHub repository for the development of a 64-bit multicore PolarFire SoC here. The FPGA SoC is equipped with a 5-core Linux®-capable processor subsystem based on the RISC-V ISA. Its simulation in Renode supports a wide range of peripherals, starting with low-speed communication interfaces like SPI, through USB and PCIe® support, to hardware-accelerated cryptography. Additionally, as mentioned before, users can benefit from Renode’s co-simulation capabilities, allowing them to use their Verilog code as simulation models within the Renode environment.

Microchip also provides a low-cost development platform—the Icicle Kit, which is supported in Renode as well. You can easily run it using only one command in the Renode CLI:

```

start @scripts/single-node/icicle-kit.resc

```

This simulation runs Yocto-based Linux with a full bootloader flow to be as close to the physical hardware experience as possible.

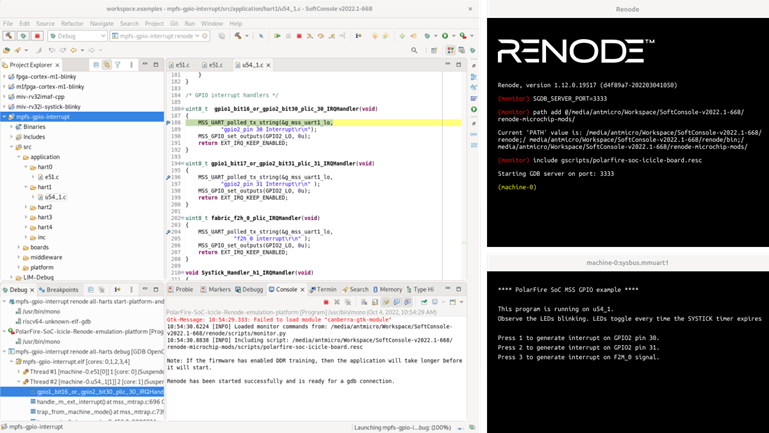

Integration With Microchip SoftConsole

Microchip provides an Eclipse-based Integrated Development Environment (IDE) for developing bare metal- and real-time operating system (RTOS)-based C/C++ software called Microchip SoftConsole, which has been integrated with Renode as part of our cooperation. This integration is based on GDB support in Renode and as a result, Renode now ships as an integrated part of SoftConsole. This allows you to start the debugging of your system with just a single click, both on Mi-V soft CPU cores and the PolarFire SoC FPGA. This pairing is especially effective considering Renode lets you run the same unmodified binaries you would use on the target hardware.

Renode for Microchip’s Microcontrollers (MCUs)

The list of Microchip’s hardware supported in Renode extends far beyond the PolarFire SoC FPGA, the Icicle board and Mi-V Soft CPU cores. Many of Microchip’s Arm Cortex®-M-based MCUs, like the SAM E70, can also be simulated along with their peripheral interfaces, including network connectivity. Specifically, as part of Antmicro’s work with SAM E70, we have implemented Time Sensitive Networking (TSN) and Precision Time Protocol (PTP) for building time-critical control systems in Zephyr and Renode. TSN is being widely deployed in robotics, industrial, railway and other systems, and thanks to Antmicro’s previous open-source work you can build TSN-enabled products with end-to-end simulation testing using Renode and Zephyr RTOS.

To see the complete list of Microchip platforms supported in Renode, visit Renodepedia and Microchip’s vendor page or see the status of Zephyr-supported Microchip platforms in the Renode Zephyr dashboard.

Antmicro’s Hardware and FPGA Engineering Services

In addition to providing first-class support for Microchip’s products in Renode, Antmicro is building real-world FPGA and hardware systems, developing open source FPGA IP, software and boards such as a dedicated HDMI breakout board that connects to Icicle’s RPi expansion header and aims to enable a Linux-FPGA platform in their products.

Build Your Next Project With Mi-V Ecosystem Partner Antmicro

Antmicro’s long-lasting partnership with Microchip enables us to provide deep experience in developing hardware, software and testing solutions around the Mi-V ecosystem—watch out for new developments in this space at this year’s RISC-V Summit, where Microchip is a Platinum sponsor, while Antmicro will be highlighting many of Renode’s co-simulation features and RISC-V support in the ML co-development with RISC-V and Renode talk together with Google.

Antmicro offers commercial support and engineering services around Renode, Verilator and other tools, as well as FPGA and ASIC design, hardware, software and cloud services. If you want to discover how Antmicro can help your state-of-the-art product hit the market, do not hesitate to contact us at contact@antmicro.com.