Matching A/D Converter Performance with Application (Part 3)

A fundamental understanding of precision and accuracy and how they relate to ADC specifications enable the designer to quickly choose the right ADC quickly for their application.

In part one of the article series, we described a customer problem. Sometimes individuals run into an issue where they are not able to get the accuracy expected in their system even though they selected what appeared to be an appropriate level of performance in the ADC. In part two we defined the ADC parameters that affect precision and accuracy.

In part three, we will look at how and why ADC parameters vary.

In our example, the customer used a 12-bit resolution ADC integrated with an MCU for their test system that they thought would give them the performance they needed to meet the system requirements. Integration is the best friend of functionality. Integration allows more functions to be added to a device, which reduces system size and cost. But the enemy of integration is performance. In the MCU that the customer chose, there are over 30 functions integrated into the MCU with the ADC being one of them. Having to accommodate that many functions in a single-chip means managing compromises in performance.

How is performance impacted by integration? Let’s take a look at four contributing factors that led to compromises in ADC performance: integration itself, test capability, temperature variation, and process technology.

Integration

The first challenge that will affect the performance of the ADC is integration. The MCU will be sitting right next to the perfectly designed ADC. The fast-switching MCU will introduce switching noise and ground bounce into the ADC circuit. Ask any experienced analog designer about circuit layout issues affecting analog performance at a board level and he will tell you stories of tragedy that will rival any Shakespearian play. Now imagine the board size is reduced to the area of an IC and the issues become exponentially more difficult to address. Clock synchronization and management techniques can be used to minimize these effects, but the interaction of peripherals and asynchronous events will still impact ADC performance.

Test Capability

The second challenge is the test capability. Microcontrollers (MCUs) are digital devices and, as such, they are tested on digital test platforms using digital test vectors. The digital test solution is optimized for the shortest test time to get the most volume of units through test in the least amount of time. These test platforms often have limited, low performance analog test capability. That is why the specifications of analog peripherals on microcontrollers are either “guaranteed by design” or “guaranteed through characterization”. These testers are often only capable of testing the analog function – or what the analog is doing - they do not have the capability of testing analog performance – how well the analog is performing its function. In addition, the performance limitations of the tester, limits the performance specification of the ADC. You cannot test a device specified as a 1 MSPS 12-bit ADC performance if your tester only has 100 kSPS 8-bit capability. Furthermore, to add analog test capability onto a digital test platform would require an order of magnitude increase in test cost which would have a corresponding increase in the device cost.

Temperature Variation

The third challenge is one of the worst enemies of analog performance – temperature. In a perfect world the outdoor temperature would always be 72°F, and electronics would always operate at 25°C, but neither happens. As electronics moves closer to the sensor, the operating temperature of the electronics changes, in some cases varying more than 100°C. This temperature change can negatively impact electronic circuits – especially analog circuits. Imagine if you designed the perfect ADC, and then you added a temperature source next to it. Now imagine that the temperature source varied, sometimes hot and sometimes warm. That would wreak havoc on your ADC performance. That is exactly what an MCU next to an ADC is doing. Going from high-speed active power (hot) to standby, sleep or hibernate (not so hot) and in order to get predictable performance in this environment, temperature compensation circuitry needs to be added. This would increase size and cost, a luxury that ADCs integrated with MCUs typically do not indulge in.

Process Technology

The fourth challenge is the process technology. Since the main function of the device with the integrated ADC is the MCU, it makes sense that the process technology used is an MCU-friendly process. After all, customers are paying for the MCU and the ADC is just a peripheral, so it does not make sense to choose a process optimized for just a peripheral on the device.

MCU’s are typically designed on smaller geometry processes which offer good digital density and high-speed transistors. The benefit to the ADC is that using such a process will reduce the size of the ADC. The small geometry process may reduce the size of the ADC, but the overall cost of the ADC may actually increase due to the substantially higher cost of the process. However, the higher die cost is more than offset by the lower test cost.

Furthermore, by limiting the size of components available on the process, the ADC noise will increase, specifically thermal noise, or kT/C noise. Larger capacitors are used in ADC designs to reduce thermal noise, which is a significant design constraint on a smaller geometry process. In fact, it is geometrically more challenging to implement the components needed for analog performance on smaller geometries. In addition, smaller geometry capacitors introduce leakage, non-linearities and matching issues that are not as controlled as they are in larger geometry processes. The same goes for transistors. This lack of control will ultimately lead to manufacturing process variations which will show up as parametric variations in the performance of the ADC.

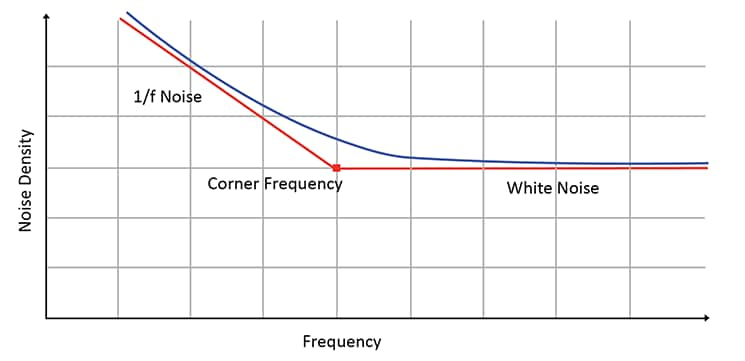

Another challenge with smaller geometry processes is 1/f noise. 1/f noise dominates at low frequency and decreases from DC by roughly a factor of 1/SQRT (frequency). At higher frequency, white noise starts to dominate the 1/f noise at a point called the corner frequency as shown in Figure 1. (Spoiler alert!) If you want to improve performance by using digital compensation techniques such as averaging or oversampling, you need to ensure that you are only sampling values that contain white noise and not 1/f noise. The problem for smaller geometry processes versus larger geometry processes is that the corner frequency shifts higher – significantly higher. This is precisely why digital filtering techniques such averaging, or oversampling do not improve system performance in systems with high 1/f corner frequencies, in fact, in some cases, digital filtering techniques can decrease system performance. In essence, it does not matter how good the ADC design is, the limitations of the process will ultimately dictate the achievable performance of the ADC.

How do these contributing factors impact ADC performance and ultimately system performance? In part four, we will go back to our original customer problem and see how these contributing factors impacted the system performance.

To read continued articles on this matter: