Zero-Drift Amplifiers: Taking the Good With the Bad

The use of zero-drift amplifiers continues to grow due to the superior dc precision that these devices offer. However, there is a downside to this performance – time domain limitations.

Zero-Drift Amplifiers: Taking the Good (Precision) with the Bad (Time Domain Performance)

Zero-drift amplifiers, meaning amplifiers that implement a continuously self-correcting architecture, have received a lot of fanfare due to the high level of dc precision that they enable. Although this attention is well deserved, there is a down-side to this superior precision – namely, the amplifiers time domain performance.

The Basic Architecture of Zero-drift Amplifiers

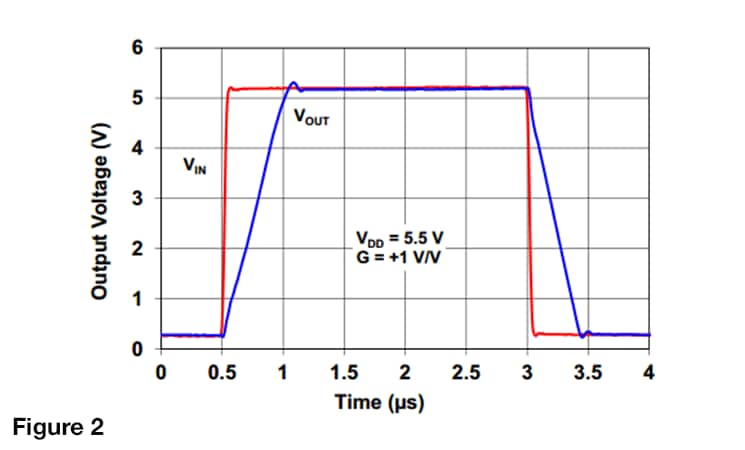

Before delving into the time domain aspects of these zero-drift amplifiers, it’s beneficial to review the basic architecture used within many of these devices. Figure 1 provides a high-level look at a chopper-stabilized architecture, such as that used on many of the MCP6Vxx zero-drift amplifiers from Microchip.

Figure 1. A chopper-stabilized architecture.

The chopper-stabilized amplifier has two signal paths, a high bandwidth path that is always connected to the main amplifier and a lower bandwidth auxiliary path. The main amplifier is designed for high bandwidth and determines the specified gain bandwidth product and slew rate of the overall amplifier. The input signal is also routed through the auxiliary path, which has chopper switches at both the inputs and the outputs, followed by a filter stage before being added back to the main amplifier path. The auxiliary amplifier in this secondary path has extremely high gain, enabling it to correct offsets from millivolts down to microvolts.

How the Architecture Affects Time Domain Performance

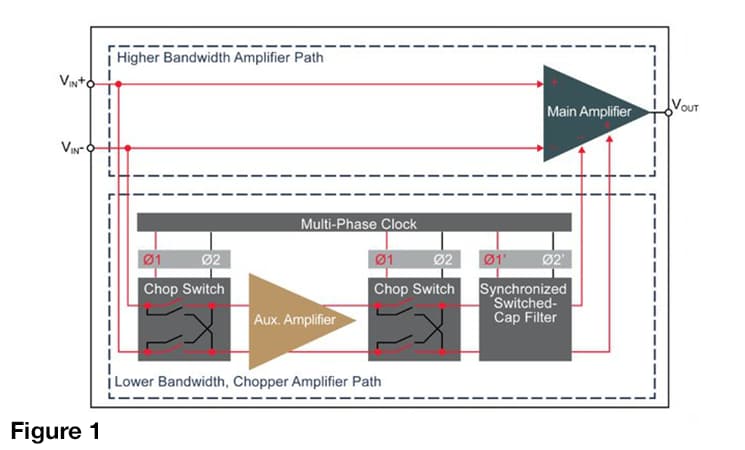

Now that we have a fundamental understanding of this architecture, let’s explore how this affects the time domain performance of the amplifier. Let us first consider a large-scale step response on the input of the amplifier, as seen in figure 2.

Figure 2. Large-scale step response.

In this example, the input voltage (shown in red) is stepping from approximately 200 mV up to 5.2V nearly instantly. The output voltage of the unity gain amplifier (shown in blue) attempts to match this step response but is slew limited and takes additional time for the output to settle to its final value. This is an especially difficult situation for self-correcting architectures. As discussed earlier, the higher-bandwidth signal path within the zero-drift amplifier is responsible for the overall speed (gain bandwidth and slew-rate). However, once the new value of a step response is reached, the output has to then settle to within the low offset limits of the zero-drift amplifier (typically less than 50 µV). This involves the bandwidth-limited, auxiliary path and, therefore, is largely a function of the chopping frequency. The use of higher clock frequencies has enabled relatively fast settling times, but for zero-drift amplifiers, these are typically in the tens of microseconds or higher. However, higher chopping frequencies can lead to an increase in the final corrected offset voltage, which typically takes priority for precision designs.

Another time domain aspect of zero-drift amplifiers that must be considered is startup behavior. When the amplifier first powers up, there is a brief period of time in which the output of the amplifier will reflect the uncorrected offset error of the main amplifier (as shown in the previous figure above). Once the supply voltage reaches the trip-point, as defined by the amplifiers power-on reset circuitry, the auxiliary correction path requires a few clock cycles before the output of the main amplifier is back within the specified offset levels. Typically, this start-up time is well within the start-up time of the entire system in which the amplifier operates, and therefore isn’t an issue. However, if the amplifier is configured for high closed loop gain, the momentary uncorrected offset (which may be as high as ±5 mV) at the output of the amplifier may cause the amplifier to rail. In this case, the start-up time will also need to include the time it takes for the amplifier to return to its linear operating region. For Microchip zero-drift amplifiers, a typical value for this overdrive recovery time is provided in the datasheet.

Understanding How Amplifier Architecture Affects Time Domain Performance Can Help Avoid Design Pitfalls

Modern day zero-drift designs have strived to make these time domain trade-offs as small as possible, but it is still worthwhile for the system designer to be aware of these potential issues. Extended start-up time and overdrive recovery can affect other timing related functions within the system, such as the appropriate time for an analog-to-digital converter to sample a signal. By understanding these potential issues and how they are related to this unique architecture, a designer can compensate for these issues in the initial design, as opposed to tracking down timing related issues after the design is complete.

Click here to learn more about Microchip’s line of operational amplifiers, including zero-drift amplifiers.