FIL Workflow

Our integrated FIL workflow with MathWorks® enables a unified workflow to verify designs comprehensively. It integrates Libero® SoC Design Suite with MATLAB® and Simulink® for design verification and provides FIL verification with our FPGA boards. This helps you catch bugs early in the design cycle, reduce time to market and enable early verification.

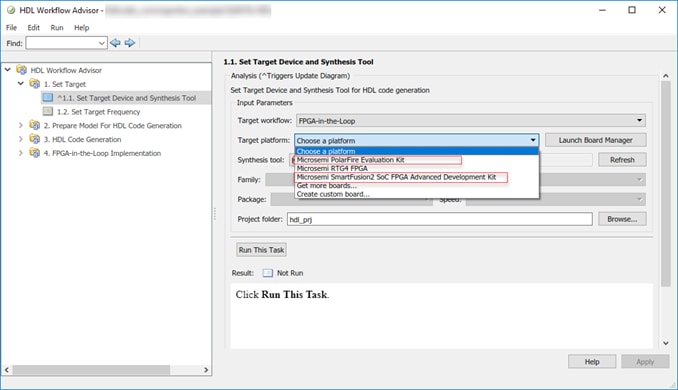

The integrated FIL workflow with MathWorks’ HDL Coder™ and HDL Verifier™ automatically generates test benches for HDL verification, including VHDL and Verilog, providing rapid prototyping and verification of designs.

The workflow is now available in the R2020A MATLAB release with Libero SoC Design Suite v12.0. This integrates MathWorks’ MATLAB and Simulink with our RTG4™ FPGA Development Kit, PolarFire® FPGA and SmartFusion® 2 System-on-Chip (SoC) FPGA development boards for FIL verification..

MathWorks’ HDL Workflow Advisor is a guided tool to help you generate the HDL code with HDL Coder, deploy the bit stream directly on the PolarFire and SmartFusion 2 FPGA evaluation boards and connect these boards directly with MATLAB and Simulink system-level test benches using HDL Verifier. This FIL simulation helps engineers validate critical systems and other applications for aviation and defense directly on the PolarFire and SmartFusion 2 FPGAs in one unified environment.

|

Title

|

|

|---|---|

| Generating the HDL Code and Running the FIL Simulation | Download PDF |