Why Is Power Sequencing Needed?

During the startup and shut down of system power supplies to digital MOS semiconductor devices, it's important to prevent the unintentional application of power in a way that can cause power spikes, bus contention or even destructive latch-up conditions. The use of a controlled application of power in a predetermined sequence is one way to control the power supply behavior and prevent those unintended behaviors.

Solve the Power Sequencing Needs of the System Designer

During the startup and shut down of system power supplies to digital MOS semiconductor devices, it's important to prevent the unintentional application of power in a way that can cause power spikes, bus contention or even destructive latch-up conditions. The use of a controlled application of power in a predetermined sequence is one way to control the power supply behavior and prevent those unintended behaviors.

Logic Interconnection Between Two or More Internal Voltage Domains

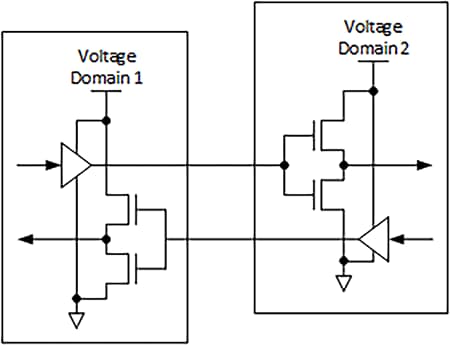

When the input voltage to a MOS semiconductor device ramps up before the power supply of the MOS device, there is the chance of the circuit exhibiting undesirable behavior. This behavior is often associated with digital devices, as analog devices are less susceptible on startup or shut down in an uncontrolled manner. Figure 1 shows an example situation in which this type of problem can occur; note that the two voltage domains can be across separate devices or across a monolithic device such as an FPGA where logic signals must cross between two or more internal voltage domains.

Figure 1 – Logic Interconnection between Domains

Prevent Unconstrained Startup Sequence

When the devices are in a power down state, all nodes are at 0V and there is no source of power, meaning no current flows in the circuit. This is the initial condition at startup and if there are no constraints applied to a startup sequence, each domain’s voltage will rise at power up as a function of each voltage regulation circuit, the load that the regulator sees, the system filtering and bypass capacitors and other design-specific considerations so there are no limits to how fast the voltage will rise and how far apart the two voltages can become. This is important since keeping power supplies less than a diode drop (<0.7 under nominal conditions, <0.3V over temperature) is one of the conditions that we want to prevent at startup and during operation in many cases. The regulator’s specifications cannot accurately predict the voltage rise time since the load in the system will be different from the one assumed by the test conditions by the data sheet.

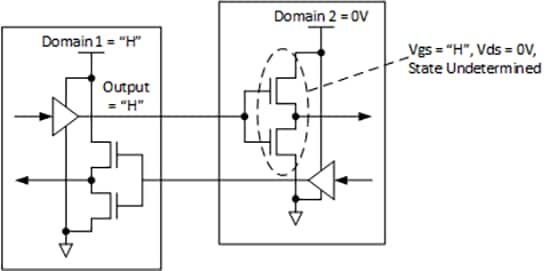

Figure 2 shows an example of the situation that can occur when the power supply for an output comes up before that of a MOS digital input and the output wants to pull up to the “H” voltage while the power to the input side is still at 0V. When this occurs, the state of the MOS input transistors is undetermined and there are a variety of things that can occur because of this which include a phenomenon known as “latch-up.”

Figure 2 – Unconstrained Startup Sequence

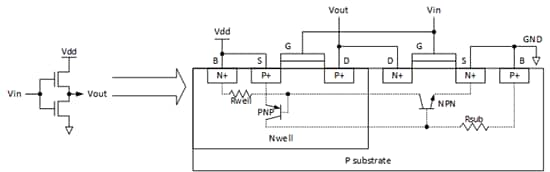

Logic Gate Schematic and Its Matching Layout

Latch-up occurs when the applied voltage causes a Bipolar Junction Transistor (BJT) to turn on unexpectedly, connecting the power to ground or some other lower potential through a low impedance connection. The BJT can be an intentional one (part of the design) when the BJT is forward biased due to an unexpected voltage condition, but most often in a monolithic MOS IC it is an unintentional one formed by intrinsic parasitic PN junctions that exist. When two such parasitic PN junctions form a PNPN device such as a Silicon-Controlled Rectifier (SCR) or thyristor, they can latch up and result in very high current flow, causing localized heating of the IC which can cause permanent damage. See Figure 3 for an example of a typical logic gate schematic and its matching layout showing the resulting parasitic circuit in dashed lines.

Figure 3 – Example Logic Gate Schematic and Layout

When the power is applied in the proper sequence, these parasitic circuits are benign unless triggered. When a trigger source is provided by natural sources, such as ionizing radiation, that can trigger a latch-up, but in most terrestrial usage cases this is exceedingly rare; space applications are one such example where there is a real need for radiation-hardened designs. In typical usage, a source of overvoltage or current injection is needed to trigger the SCR creating the need for a well-controlled startup sequence to prevent the trigger source from being provided during startup. Once the latch-up is triggered, the only way to stop it is by removing the applied voltage and interrupting the current flow.

Another way a damaging condition can occur on power up is when the input is part of a separate IC where an ESD protection device is part of the design. These typically have maximum input voltage rating which specifies that the maximum voltage at the input can only exceed the supply by a small voltage like 0.3V. This is to keep the input voltage from exceeding the turn-on voltage of the ESD device. When the ESD device is forward biased, large currents to flow from the pin to the power supply connections of the device and can damage it.

These are only the most damaging examples of what can happen when start up sequences are uncontrolled; there are other situations that can arise where physical damage is not the issue. Bus contention, glitching, dropouts and other types are less damaging but annoying behavior can occur when voltage potential differences during power cycling occur.

Many sources of information say that a proper startup sequence is one where the core logic voltage comes up first, followed by the input/output voltage and peripheral devices. Starting up from the inside out this way is only a rule of thumb; however, the way the ESD network is connected in the product for example can mean that the standard rule-of-thumb assumption is not appropriate. Each product’s documentation should be checked for what the recommended startup sequence is and then the total system startup sequence worked up from converging all those requirements together. It should be noted that there can be situations where there is residual power stored in the system bypass and filter capacitors at start up time, which can complicate the startup. This can occur when power is interrupted briefly, called brown-out, and then power is reapplied before the system supplies are completely discharged. It can also happen in systems where, for whatever reason, the system is not fully discharged when power is supplied. This is where shutdown sequencing can be needed to ensure an orderly shutdown that does no damage and to ensure that the system is left in a safe state for startup. A detailed treatment of shutdown sequencing is beyond the scope of this blog post, but in general the proper sequence for shut down is to reverse that of a startup sequence.

It can be difficult to implement power sequencing using only discrete power management devices; they typically do not have the feature set to support complex power sequencing in coordination across multiple power rails. Designing such a solution takes some significant engineering effort, typically requires extra components, and can involve some risk in production if there are any design sensitivities that were not found in pre-production testing.

Integrated Power Management (PMIC) With Built-In Support for Power Sequencing

An alternative is the use of a more integrated PMIC that has built-in support for power sequencing along with other functionality that can be useful in these situations. Note that not all PMICs have these features and since there is no one-size-fits-all approach to power sequencing, when they have these features, they may not be exactly right for a given design, but when they do, they provide an efficient solution to using handful of discrete devices.

Our PMICs (Power Management ICs) such as the MCP16501 and MCP16502 are designed with startup and shutdown power sequencing in mind and have features that support the functionality needed by the SAMA5DX/SAM9X60/SAM7G systems. The MIC7400 and MIC7401 are also standard product PMICs that offer power sequencing functionality that can prove useful to solving the power sequencing needs of the system designer.

Learn more about PMICs.