Live Chat

Need Help?

Privacy PolicyWe are committed to providing you with FPGAs that you can successfully use in safety-critical designs. New technology brings new ways for a system containing electronics or programmable electronics to fail. Failures can cause harm to people and property and although it is impossible to guarantee a technological system will never fail, it is possible to reduce the risk of failure and to design systems so that if they do fail, they fail safely.

We provide a TÜV Rheinland-certified Libero® SoC Design Suite to accelerate time to market and product certifications for functional safety across segments such as industrial, automotive and medical.

We support the following functional safety standards:

Products

Our FPGAs have a strong heritage in high-reliability applications deployed in space and commercial avionics. Adherence to functional safety standards is a natural extension to this heritage and our commitment towards safety and reliability. Our FPGA and SoC portfolio offer the following advantages:

Most Power-Efficient FPGAs

Two Times More Performance Per Watt

Exceptional Reliability

Zero Configuration Upsets

Product Longevity, Heritage and Service History

Customer Driven Obsolescence Practice

Libero SoC Design Suite

Libero tools offer the following key features:

- Design methodologies that support safety and non-safety designs in the same FPGA or SoC

- Design separation methodology required to implement security and safety-critical applications

- For a system to be secure and reliable, all critical subsystems in the design should be independent of each other

- Microchip Separation Verification Tool (MSVT), a stand-alone tool to verify that your design meets the requirements of the design separation criteria

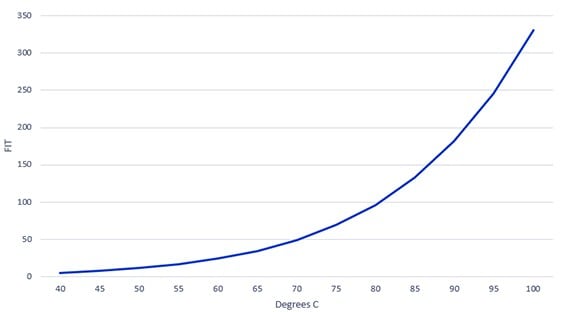

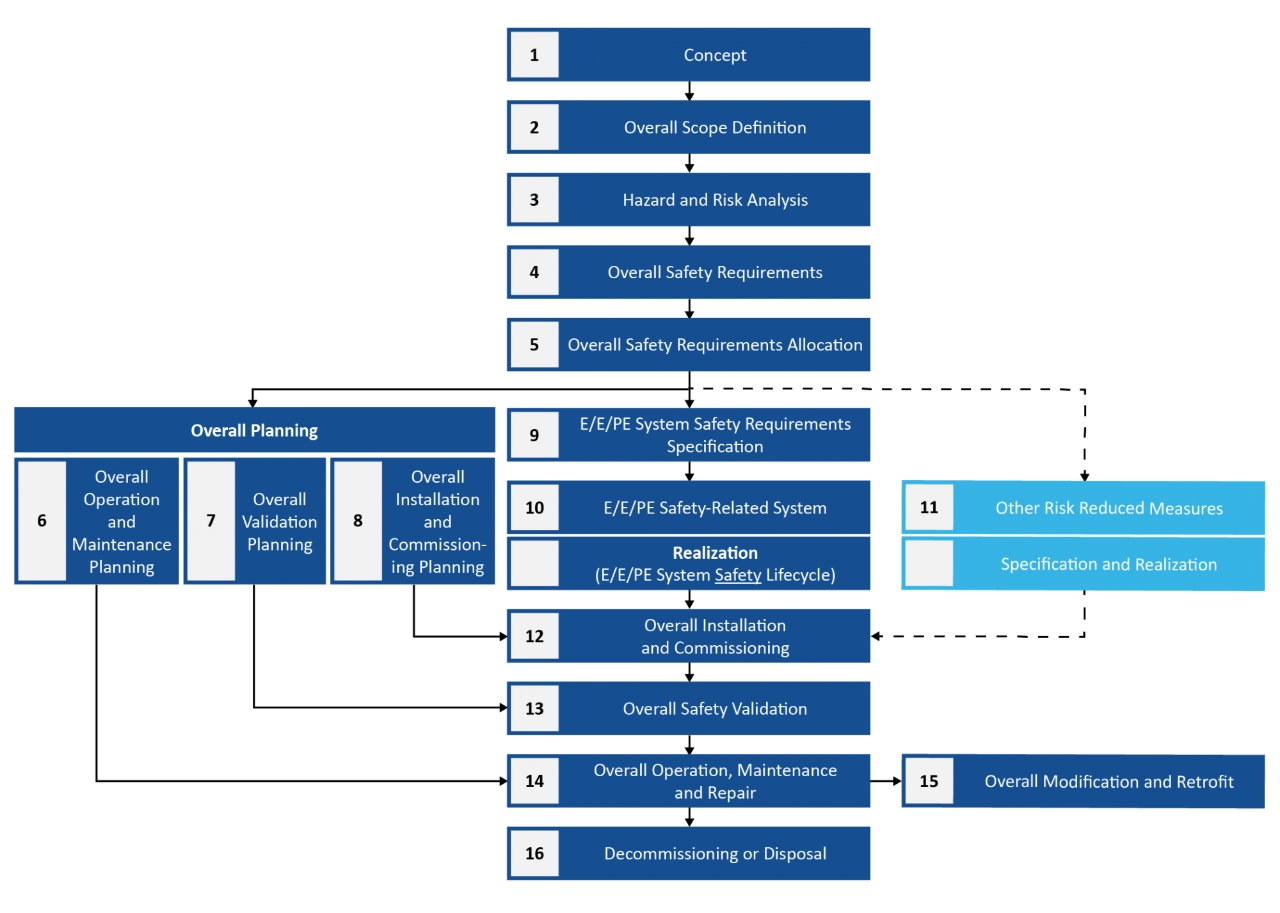

IEC 61508 Compliance

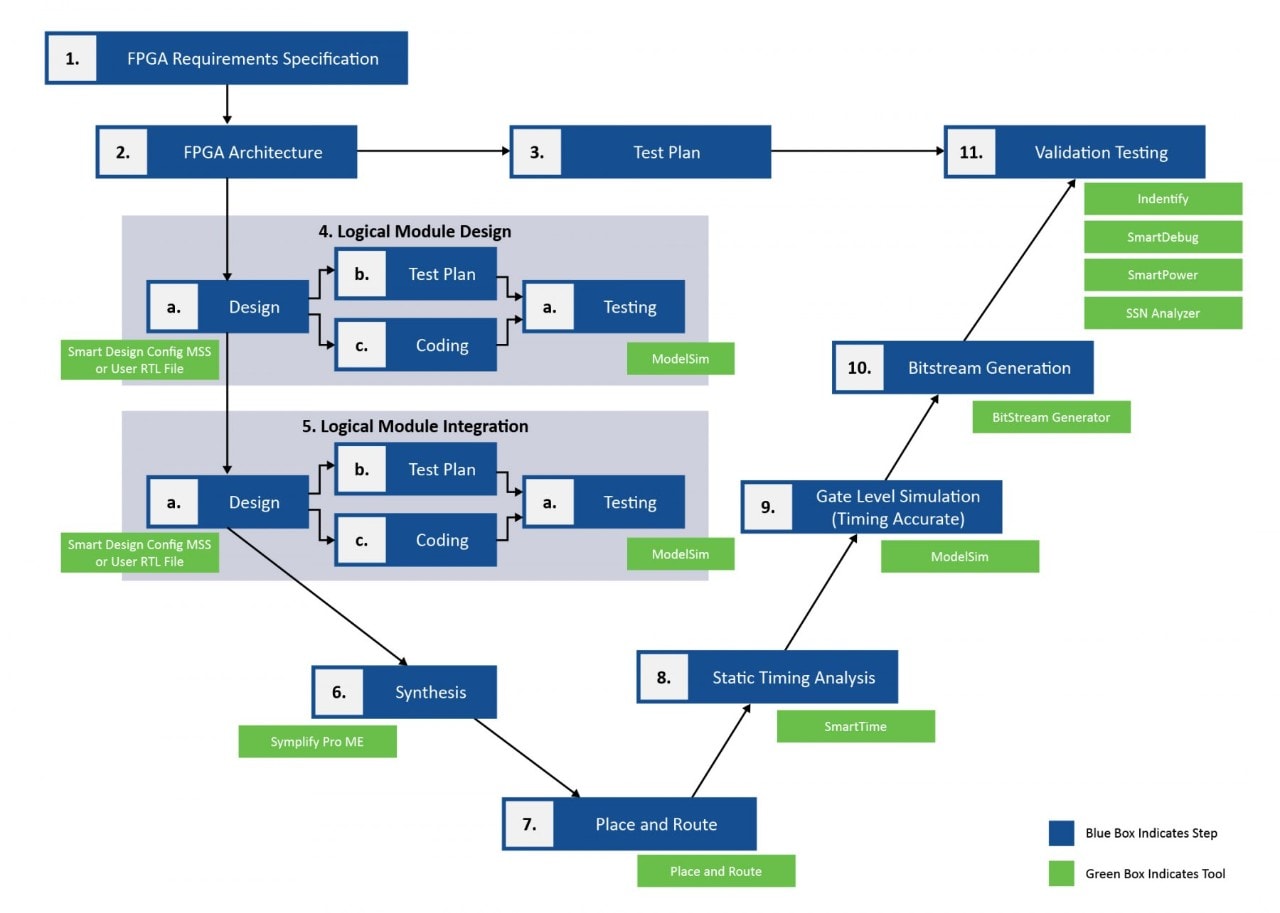

V-Model Development

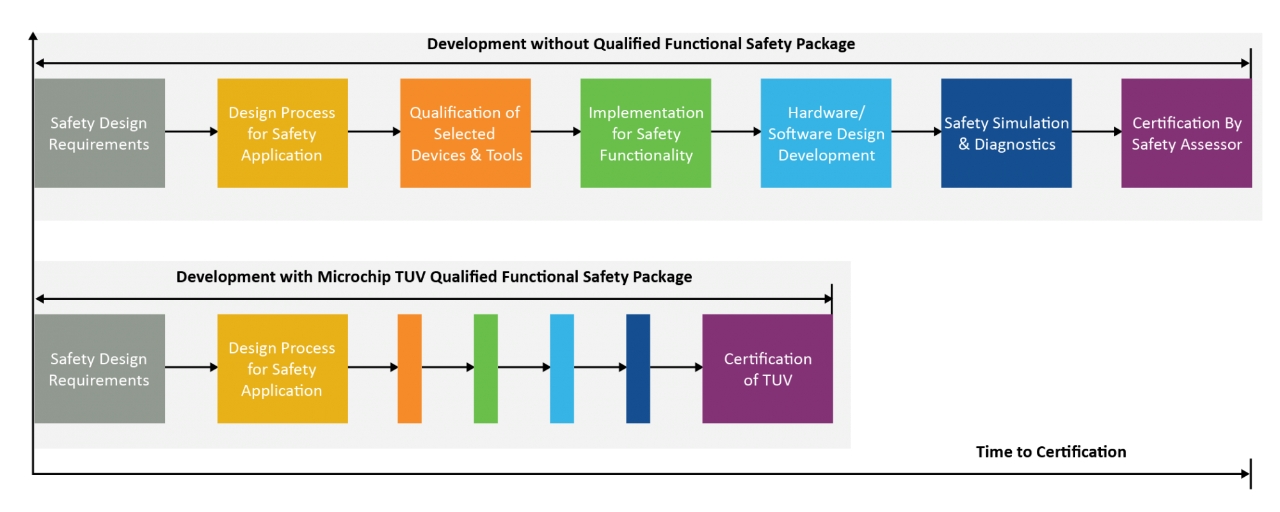

Timeline Reduction for Functional Safety

We designed the functional safety packet to assist with IEC 61508 and ISO 26262 certifications. It includes:

- Libero SoC Design Suite certified by TÜV SÜD

- Functional safety user guide

- FPGA and SoC products reliability report

- Libero SoC Design Suite documentation

- Relevant IP cores and associated documentation